Wearable-Hardware-Design scheitert selten an einem einzelnen Problem. Typisch ist eine Kombination aus falsch dimensioniertem Energiebudget, zu spätem mechanischem Abgleich und EMI-Problemen, die erst in der Zertifizierung sichtbar werden. Jeder dieser Fehler kostet zwischen zwei und acht Wochen Entwicklungszeit und eine zusätzliche PCB-Iteration. Dieser Artikel benennt die häufigsten Ursachen, erklärt die jeweiligen Konsequenzen und zeigt, unter welchen Bedingungen welche Gegenmaßnahme sinnvoll ist.

Table of Contents

ToggleWarum scheitern so viele erste Wearable-Prototypen in der Praxis?

Der häufigste Auslöser ist nicht fehlende Kompetenz, sondern fehlende Parallelisierung. Schaltkreis, Firmware und Mechanik werden sequenziell entwickelt, obwohl ihre Wechselwirkungen früh entschieden werden müssen. Thermik beeinflusst das Energiebudget. Das Energiebudget beeinflusst die PMIC-Auswahl. Die PMIC-Auswahl beeinflusst das PCB-Layout. Wer diese Abhängigkeiten erst beim mechanischen Zusammenbau auflöst, zahlt mit einer vollständigen Layout-Iteration.

Ein weiteres strukturelles Problem: Teams unterschätzen den Abstand zwischen einem funktionierenden Laborprototypen und einem serienreifen Design. Serienreife erfordert reproduzierbare Fertigungstoleranz, Robustheit unter Körperbedingungen und Zertifizierungskonformität. Alle drei Anforderungen sind im Prototypenstadium oft vollständig unberücksichtigt, was späte und teure Korrekturen erzwingt.

Welche Fehler beim Energiemanagement verkürzen die Akkulaufzeit von Wearables?

Falsch dimensionierte Spannungsregler, unvollständige Sleep-Mode-Implementierungen und nicht deaktivierte Peripherieschnittstellen sind die drei häufigsten Ursachen für reale Akkulaufzeiten, die um Faktor zwei bis fünf unter den theoretischen Berechnungen liegen. Alle drei Fehler entstehen durch fehlende systematische Strombudgetanalyse vor dem ersten Layout.

Falsch dimensionierte Stromversorgung

Ein LDO zwischen einem 3,7-V-LiPo und einem 1,8-V-Core wandelt die Spannungsdifferenz vollständig in Wärme um. Bei 50 mA Laststrom bedeutet das 95 mW thermische Verlustleistung, die in einem miniaturisierten Gehäuse weder abgeführt werden kann noch akzeptabel ist. Buck-Converter oder integrierte PMICs mit Wirkungsgraden über 85 % sind in diesem Szenario die korrekte Wahl, erhöhen jedoch die Layoutkomplexität und erfordern sorgfältige EMI-Maßnahmen. Wer den LDO wählt, um das Layout zu vereinfachen, erkauft sich das mit einer messbaren Reduktion der Akkulaufzeit und einem Thermikproblem, das im Gehäuse eskaliert.

Fehlende oder fehlerhafte Sleep-Mode-Implementierung

Unvollständige Sleep-Mode-Implementierungen sind in ersten Firmware-Versionen der Regelfall. GPIOs in undefiniertem Zustand, aktive I2C-Busse im Standby und externe Sensoren ohne Standby-Kommando erzeugen zusammen typischerweise 2–10 mA Dauerstrom. Bei einer 300-mAh-Zelle bedeutet das eine Laufzeit von 30–150 Stunden statt der projektierten Werte. Eine Strombudgetanalyse mit einem Präzisionsmessgerät wie dem Nordic Power Profiler Kit II sollte ab dem ersten funktionsfähigen Firmware-Build Pflichtbestandteil des Testprotokolls sein.

Unterschätzte Ruheströme

Spannungsregler, Ladeverwaltungs-ICs und Funkmodule haben Ruheströme im Bereich von 10–500 µA pro Baustein. Werden diese Werte im Schaltplan-Review nicht explizit summiert und gegen das Energiebudget geprüft, überschreitet der Gesamtruhestrom das Budget regelmäßig um Faktor zwei bis drei. Besonders Funkmodule mit aktivem Empfangspfad tragen hier mehr bei als ihre Datenblatt-Typtypwerte suggerieren, da diese unter Idealbedingungen gemessen werden.

Wie wirken sich Formfaktor-Fehler auf die Serienreife eines Wearables aus?

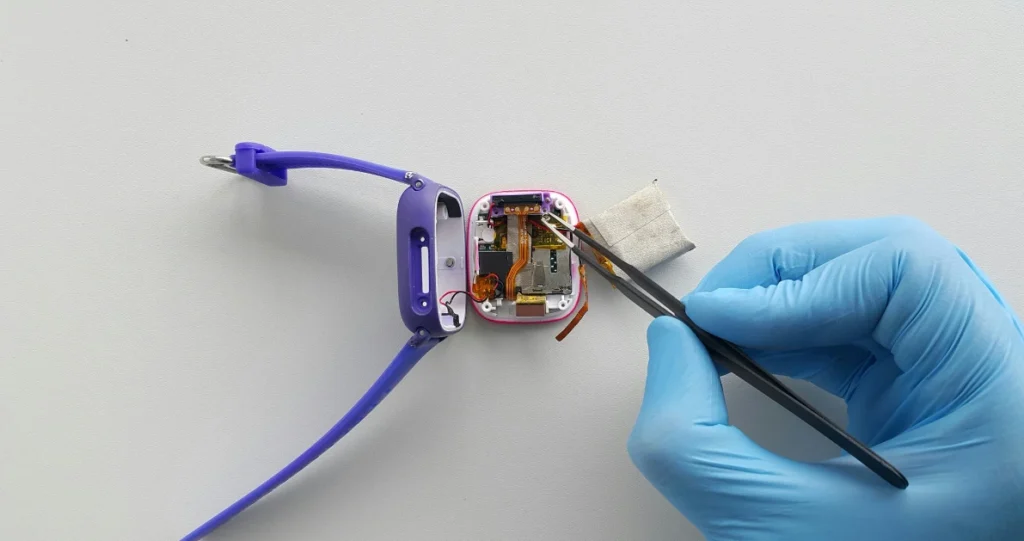

Formfaktor-Fehler werden typischerweise erst sichtbar, wenn mechanische und elektronische Baugruppe erstmals zusammengeführt werden, meist in Woche 10–16 eines Projekts. Zu diesem Zeitpunkt erzwingen Kollisionen zwischen Bauteilhöhen und Gehäuseinnenmaßen, falsch positionierte Stecker oder unzureichende Biegezonen bei Flex-PCBs eine vollständige Layout-Iteration. Jede dieser Iterationen kostet vier bis acht Wochen und 3.000–8.000 € für Prototypenleiterplatten und Bestückung.

Die Ursache ist strukturell: Mechanisches und elektrisches Design werden in getrennten Werkzeugen entwickelt und erst spät zusammengeführt. Ein gemeinsames 3D-Modell aus ECAD-MCAD-Integration, das Bauteilhöhen, Gehäusekonturen und Steckerposition von Beginn an synchronisiert, verhindert diese Klasse von Fehlern. Das ist kein optionaler Prozessschritt, sondern eine Voraussetzung für eine erste Hardware-Version ohne mechanische Überraschungen.

Die Akkuformatwahl muss in dieser Phase ebenfalls festgelegt werden. Runde Zellen sind mechanisch robuster und günstiger, aber schwer in flache Gehäuse unter 12 mm Bauhöhe zu integrieren. Pouch-Zellen ermöglichen flachere Designs, sind jedoch empfindlicher gegenüber Druckbelastung und Biegung, was bei Wearables mit flexiblen Gehäuseelementen zu Zellschäden führen kann. Diese Entscheidung beeinflusst PCB-Geometrie, Halterungsdesign und Sicherheitsschaltung und lässt sich nach dem ersten Layout nicht mehr kostenneutral ändern.

Welche EMI/EMC-Fehler sind bei Wearable-Designs besonders kritisch?

Miniaturisierte Layouts mit mehreren Funkschnittstellen und direktem Körperkontakt erzeugen eine elektromagnetische Umgebung, die sich von stationären Geräten grundlegend unterscheidet. Unzureichende Masseführung, falsch platzierte Antennen und fehlende Entkopplungskondensatoren sind die drei häufigsten Ursachen für ein Scheitern der CE-Zertifizierung, die bei Wearables 8–14 Wochen und 5.000–15.000 € kostet, wenn sie wiederholt werden muss.

Antennenplatzierung und Körpereinfluss

Menschliches Gewebe absorbiert elektromagnetische Energie im 2,4-GHz-Band mit einer spezifischen Absorptionsrate, die die effektive Sendeleistung einer körpernahen BLE-Antenne um 3–6 dB reduzieren kann. Das entspricht einer Reichweitenreduktion von 30–50 % gegenüber Freiraumwerten. Wer die Antenne nicht mit einem Körperphantom oder einem validierten Gewebemodell simuliert, erhält in der Zertifizierungsphase SAR-Messwerte und Reichweitenwerte, die das Design nicht erfüllt. Antennen gehören an den PCB-Rand mit einem metallfreien Freiraum von mindestens 3–5 mm auf allen Seiten.

Schlechte Masseführung und Schaltreglerstörungen

Schaltregler mit Schaltfrequenzen von 1–4 MHz erzeugen Harmonische, die direkt in das BLE- oder Wi-Fi-Band fallen können. Eine unterbrochene oder schlecht geführte Massefläche überträgt diese Störungen auf empfindliche Analogschaltkreise und Funkpfade. Getrennte Analog- und Digitalmassebereiche, ein durchgängiges Massepotenzial auf einem dedizierten Layer und kurze Hochstromschleifen um den Schaltregler sind Pflichtmaßnahmen in jedem Wearable-Layout. Wer diese Punkte in der ersten PCB-Version ignoriert, riskiert nicht nur degradierte Funkeigenschaften, sondern ein Scheitern der EMV-Prüfung mit anschließendem Redesign-Zyklus.

Wann sollte man bei der Wearable-Entwicklung einen Experten hinzuziehen?

Externe Expertise ist dann wirtschaftlich sinnvoll, wenn das interne Team keine nachgewiesene Erfahrung mit energieeffizienten Embedded-Designs, Funkzertifizierungen oder miniaturisierten PCB-Layouts unter 50 cm² hat. Der teuerste Zeitpunkt für externe Unterstützung ist nach dem ersten Prototypen-Fehlschlag: Ressourcen sind verbraucht, Zeitpläne verschoben und technologische Fehlentscheidungen sind getroffen, die sich nur mit vollständiger Redesign-Iteration korrigieren lassen.

Externe Unterstützung in der Konzeptphase kostet typischerweise 20–40 % weniger als die Korrektur derselben Fehler nach dem ersten Prototypen. Ein strukturierter Entwicklungsansatz mit Design-Review-Gates nach Schaltplan, Layout und Firmware-Integration verhindert die beschriebenen Fehlerklassen, ohne den Projektzeitplan wesentlich zu verlängern.

Konkrete Indikatoren, die für externe Unterstützung sprechen:

- Kein internes Erfahrungsprofil mit BLE, Wi-Fi oder LoRa im Wearable-Kontext

- Unsicherheit bei der Auswahl von Mikrocontroller-Plattformen und RTOS-Entscheidungen unter Echtzeitanforderungen

- Fehlendes DFM- und Zertifizierungs-Know-how für CE, FCC oder MDD/MDR

- Projektzeitplan unter 12 Monaten bis zur Serienreife ohne vorherige Wearable-Erfahrung im Team

- Erster Hardware-Prototyp zeigt nicht reproduzierbare Ausfälle oder Energieverbrauch, der mehr als 50 % über dem projektierten Budget liegt

Wie Oxeltech bei der Wearable-Hardware-Entwicklung unterstützt

Oxeltech begleitet Projekte von der Konzeptphase bis zur serienreifen Hardware. Das Team hat über 20 Hardware-Projekte abgeschlossen, darunter Wearables für medizinische Überwachung und industrielle Umgebungen, und kennt die beschriebenen Fehlerklassen aus der direkten Projekterfahrung.

Konkrete Leistungsbereiche:

- Energiemanagement-Design: PMIC-Auswahl und -Integration, Sleep-Mode-Strategie auf Firmware- und Hardware-Ebene, systematische Strombudgetanalyse mit Messprotokoll

- PCB-Layout und Formfaktor: Miniaturisiertes, DFM-optimiertes Layout mit synchronisierter ECAD-MCAD-Abstimmung ab der ersten Designphase

- Firmware-Entwicklung: Energieoptimierte Embedded-Software auf FreeRTOS oder Zephyr, abgestimmt auf das Hardware-Energiebudget

- Funkintegration: Integration von BLE, Wi-Fi und LoRa inklusive Antennendesign, Körperphantom-Simulation und SAR-Vorvalidierung

- EMI/EMC und Zertifizierung: EMV-Optimierung im Designstadium und Begleitung durch den CE-Zertifizierungsprozess zur Vermeidung von Nachprüfungszyklen

Ob Sie einen ersten Prototypen entwickeln oder einen bestehenden Hardware-Fehler beheben müssen: Nehmen Sie jetzt Kontakt auf und beschreiben Sie Ihr Projekt. Sie erhalten eine erste technische Einschätzung innerhalb von zwei Werktagen.